"IMPLEMENTACIÓN DE UN RECEPTOR DE RADIO DIGITAL DE BAJO COSTO PARA REALIZAR MEDICIONES CLIMATOLÓGICAS EN LA REGIÓN MLT."

V.Vasquez<sup>1</sup>, M. Milla<sup>2</sup>,K. Kuyeng<sup>3</sup>,D. Scipion<sup>3</sup>, B.Estalla<sup>3</sup>,J.Rojas<sup>3</sup>, D.Cáceres<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Universidad Nacional Mayor de San Marcos, Lima-Perú

<sup>&</sup>lt;sup>2</sup> Pontificia Universidad Católica del Perú, Sección de Electricidad y Electrónica, Lima – Perú

<sup>&</sup>lt;sup>3</sup> Instituto Geofísico del Perú, Radio Observatorio de Jicamarca, Lima, Perú.

Implementar un nuevo sistema de recepción, usando un hardware de bajo costo y teniendo en cuenta los parámetros y modo de operación del sistema de recepción actual del radar de meteoros SIMONe.

- 1. Motivación.

- 2. Tecnología SDR.

- Concepto y Avances.

- 3. Receptor Digital.

- Selección de dispositivo SDR.

- Desarrollo del Sistema de Procesamiento Digital de Señales.

- Configuración del ADC diferencial.

- Sincronización Pruebas realizadas.

- Integración del Sistema Lógico con el Sistema de Procesamiento.

- 4. Conclusiones

### 1. Motivación

El desarrollo de un receptor digital para el radar de meteoros SIMONe busca principalmente obtener una reducción de costos e independencia tecnológica, lo que se traduce en una operación más eficiente, autónoma y económica de este sistema de radar en el Perú. Además, estos receptores permitirán ampliar la zona de estudio de dichos radares.

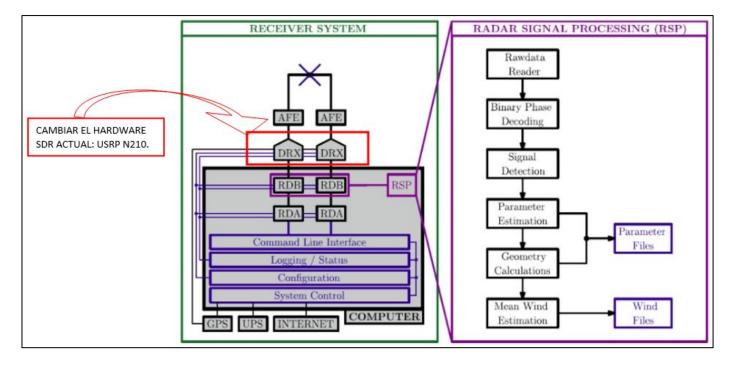

#### Receiver system - Estación de Rx del radar Simone:

**Figura 1.** "Multistatic Specular Meteor Radar Network in Peru: System Description and Initial Results. J. L. Chau (2021)".

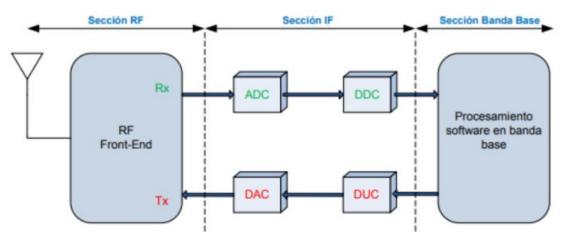

# 2. Tecnología SDR y System on Chip (SoC).

Figura 2. "Sistema de RF y SDR.

#### USRP N210

Adalm Pluto

GNURadi

Software de Procesamiento de datos OpenSource.

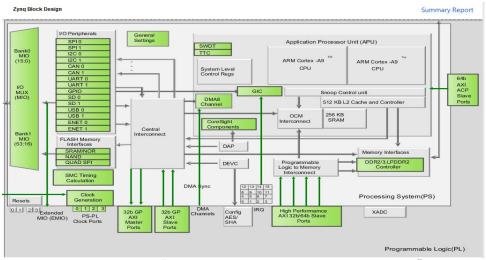

#### Zynq 7000 SoC

- Zynq 7007s: Artix®-7 FPGA +

- Zyng 7010 : Artix-7 FPGA +

- Zyng 7020 : Artix-7 FPGA +

- Zyng 7100 : Kintex-7 FPGA +

\_

Figura 3. "Dispositivo Zynq 7000"

#### Avances en la Tecnología SoC:

- Familia UltraScale: Kintex, Artix.

- Familia Zynq UltraScale: +MPSoC, +RFSoC.

**Figura 4.** "Dispositivo Zynq UltraScale +MPSoc"

#### Selección del dispositivo

Hermes

14

Búsqueda de la plataforma (Placa de de desarrollo. desarrollo)

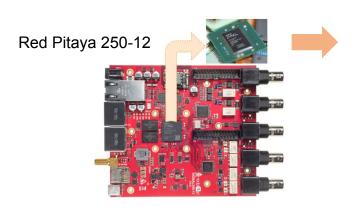

| Características /<br>Dispositivo SDR | USRP<br>N210                                                | Red Pitaya SDRLab<br>122-16 (External Clock) | Red Pitaya SignalLab<br>250-12              |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------------|---------------------------------------------|

| Canales AC Input                     | 2                                                           | 2                                            | 2                                           |

| ADC Resolución                       | 14 bits                                                     | 16 bits                                      | 12 bits                                     |

| Canales AC Output                    | 2                                                           | 2                                            | 2                                           |

| DAC Resolución                       | 16 bits                                                     | 14 bits                                      | 14 bits                                     |

| Sample Rate                          | 100 MS/s                                                    | 122.8 MS/s                                   | 250 MS/s                                    |

| Ancho de banda                       | 25 MHz (16 bits por muestra)<br>50 MHz (8 bits por muestra) | 300 KHz - 60 MHz                             | 0 - 60 MHz                                  |

| Canales Digitales                    | -                                                           | 16                                           | 16                                          |

| Software Compatible                  | <b>GNURadio</b> , MatLab,<br>Labview, Python                | LabView, MatLab, Python,<br>Scilab y Vivado  | LabView, MatLab, Python,<br>Scilab y Vivado |

|                                      |                                                             |                                              |                                             |

SIGNALIab 250-12 Standard Kit

14 122.8 MS/s 55 MHz LabView, MatLab, Python,

SDRIab 122-16 External Clock USRP N210

840,95€

★★★☆ (1 customer review

2,367,97€

**Hermes Lite 2**

\$269.00

Quartus

\$3,800.00 USD

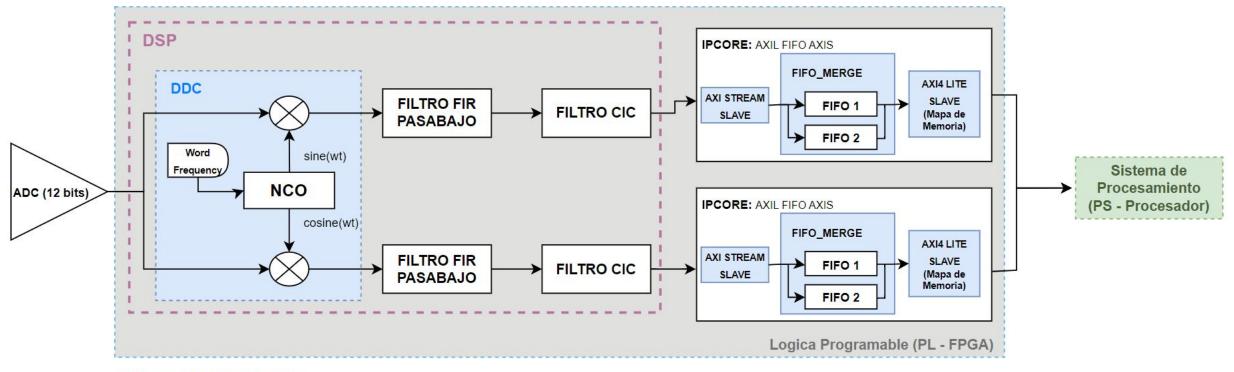

### Esquema general del desarrollo

**DDC:** Digital Down Converter **DSP:** Digital Signal Processing

Figura 5. "Esquema general del desarrollo".

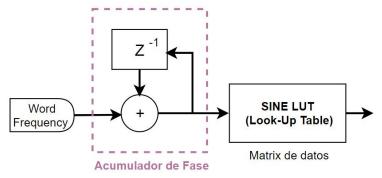

Digital Down Converter (DDC) ⇒ Oscilador Numéricamente Controlado (NCO)

Figura 6. "Arquitectura del NCO".

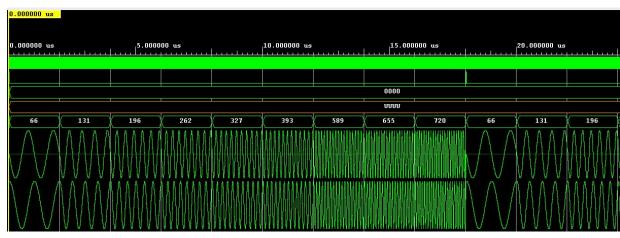

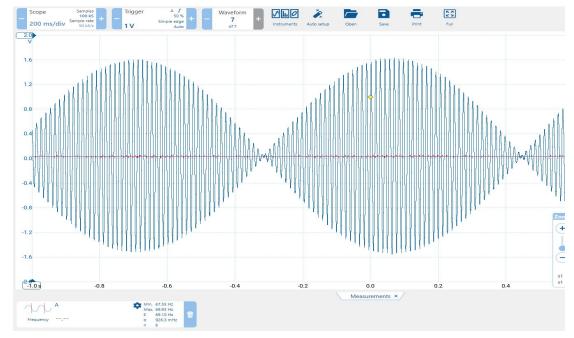

Figura 7. "Resultado en simulación del Generador de Señales".

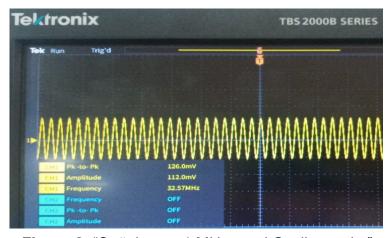

Figura 8. "Señal seno 1 MHz en el Osciloscopio.".

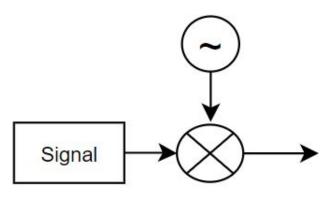

# Digital Down Converter (DDC) ⇒Demodulador

Figura 9. "Proceso de demodulación".

Figura 10. "Señal seno 1 MHz en el Osciloscopio."

#### Filtro FIR

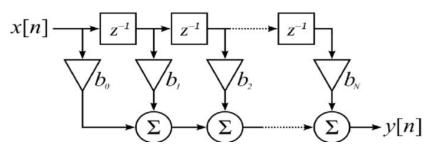

Figura 11. "Arquitectura del Filtro FIR".

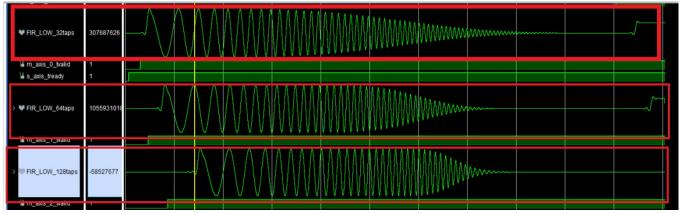

Figura 12. "Resultado en simulación del Filtro FIR para 32, 64 y 128 coeficientes, respectivamente".

#### Frecuencia de corte de 10 MHz del Filtro FIR con 64 coef..

A 4.999 MHz

Señal de 1 MHz

Señal de 5 MHz

Señal de 10 MHz

Señal de 13 MHz

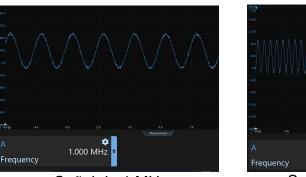

**Figura 13.** "Pruebas de laboratorio del comportamiento del Filtro FIR. Visualización de osciloscopio."

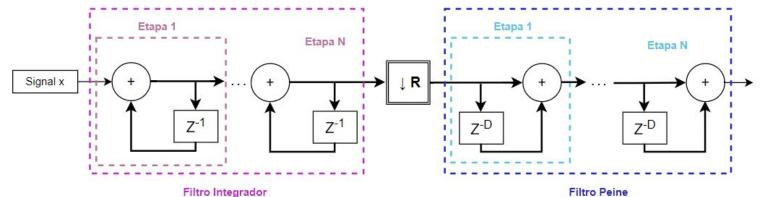

### Filtro Cascaded Integrator-Comb (CIC)

Figura 14. "Arquitectura del Filtro CIC".

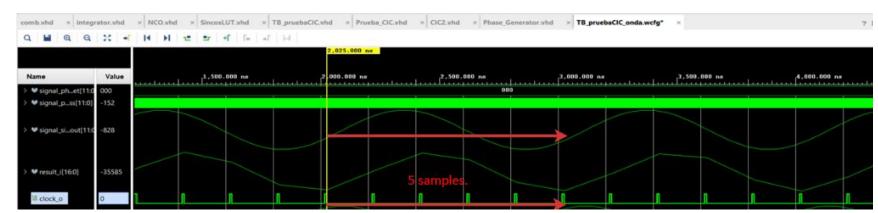

#### Prueba de simulación:

Clock: 10ns. Fs: 100 MHz. fm: 1 MHz. Dec: 20. Sample-dec= 100MHz/ **20** = **5 MHz** samples/cycle = 5 MHz / 1MHz = **5 samples/cycle**.

Figura 15. "Arquitectura del Filtro CIC".

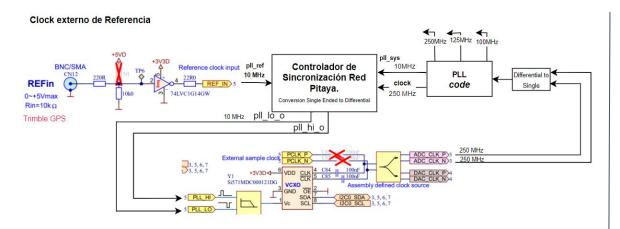

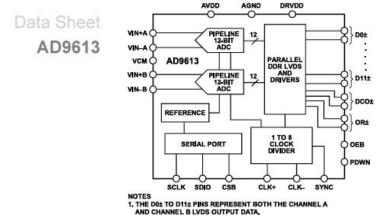

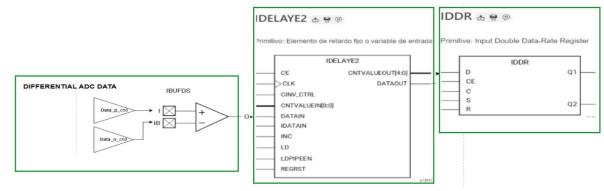

### Sincronización y Configuración del ADC

Figura 16. "Sincronización del Sistema".

Figura 17. "Diagrama del ADC".

Figura 18. "Acondicionamiento de datos diferenciales".

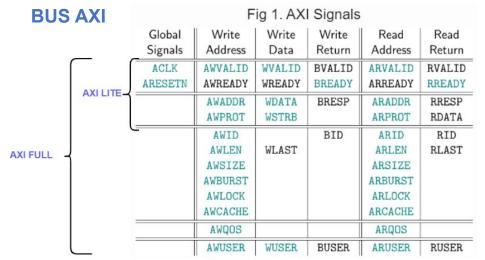

Integración del Sistema Lógico con el Sistema de

Procesamiento.

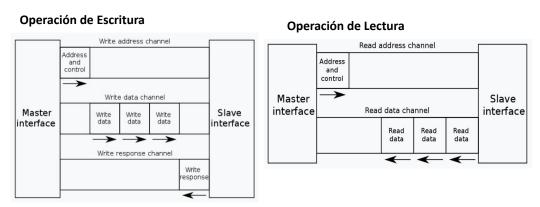

Figura 20. "Señales AXI FULL y AXI LITE".

Figura 19. "Esquema del Dispositivo Zynq7020".

Figura 21. "Operación de Lectura y Escritura del Bus AXI".

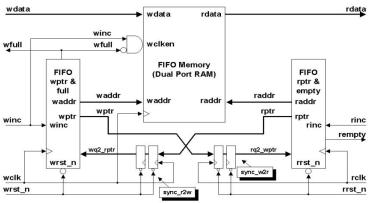

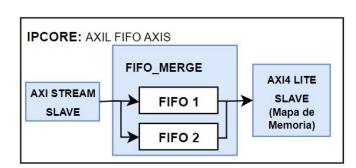

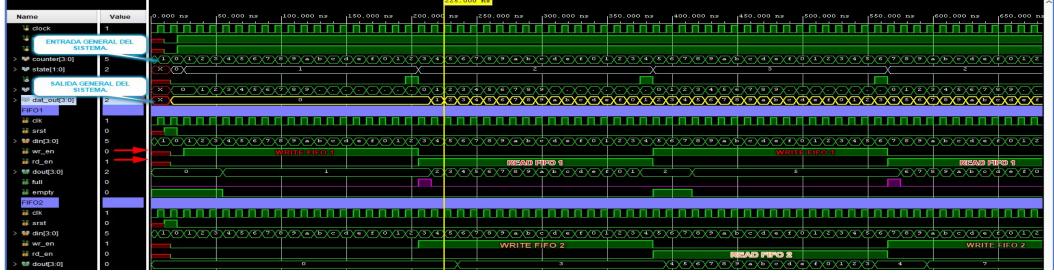

### Integración PS y PL - FIFOs

Figura 22. "Arquitectura de la FIFO Asíncrona".

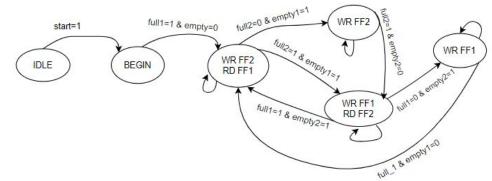

**Figura 23.** "Máquina de estado de 2 FIFOs para la Lectura y Escritura utilizando".

**Figura 24.** "Diagrama General de FIFO y Protocolos de Comunicación".

Figura 25. "Simulación del Comportamiento de Lectura y Escritura de Datos".

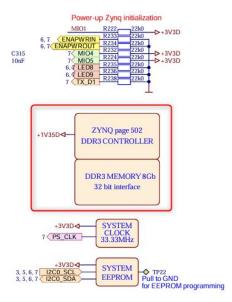

### Integración PS Integración PS y PL - Memoria DDR3

- Es necesario activar la memoria externa al utilizar periféricos que utilizan drivers con algoritmos robustos. El Zynq 7020 no tiene una memoria RAM interna grande, solo posee 256 KB.

- Los parámetros de configuración de la memoria DDR3 es cerrado, por lo que se realizó un estudio al datasheet de la memoria.

#### Zynq-7000 SoC On-Chip Memory

- On-chip boot ROM

- 256 KB on-chip RAM (OCM)

- Byte-parity support

Figura 26. "Capacidad de memoria RAM en el dispositivo".

**Figura 27.** "Datasheet de Red Pitaya sobre DDR3".

| Name                               | Select              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDR Controller Configuration       | Control Company     | AND THE RESIDENCE OF THE PROPERTY OF THE PROPE |

| Memory Type                        | DDR 3 (Low Voltage) | Type of memory interface. Refer to UG585 Zyng Technical Reference Manual (TRN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Memory Part                        | Custom              | Memory component part number. For unlisted parts choose "Custom". This will en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Effective DRAM Bus Width           | 32 Bit              | Data width of DDR interface, not including ECC data width. Refer to UG585 for a de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ECC                                | Disabled            | Enables error correction code support. ECC is supported only for an effective data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Burst Length                       | 8                   | Minimum number of data beats the controller should use when communicating wit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DDR                                | 533.333333          | Memory clock frequency. The allowed freq range is (200.000000 : 534.000000) MH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Internal Vref                      | 0                   | Enables internal voltage reference source. Disable to use external Vref pins as volt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Juntion Temperature (C)            | Normal (0-85)       | Intended operating temperature range. Controls the DDR refresh interval.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Memory Part Configuration          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DRAM IC Bus Width                  | 16 Bits             | Width of individual DRAM components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DRAM Device Capacity               | 4092 MBits (4GB)    | Storage capacity of individual DRAM components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Speed Bin                          | DDR3 1600K          | Speed bin of the individual DRAM components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Bank Address Count (Bits)          | 3                   | Number of bank address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Row Address Count (Bits)           | 15                  | Number of row address pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Col Address Count (Bits)           | 10                  | Number of column address bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CAS Latency (cycles)               | 11                  | Column Access Strobe (CAS) latency in memory clock cycles. It refers to the amoun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CAS Write Latency (cycles)         | 8                   | CAS write latency setting in memory clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RAS to CAS Delay (cycles)          | 11                  | tRCD. Row address to column address delay time. It is the time required between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Precharge Time (cycles)            | 11                  | tRP. Precharge Time is the number of clock cycles needed to terminate access to a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| tRC (ns)                           | 48.75               | Row cycle time (ns)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| tRASmin (ns)                       | 35                  | Minimum number of memory clock cycles required between an Active and Prechan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| tFAW (ns)                          | 40                  | Determines the number of activates that can be performed within a certain window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Training/Board Details             | User Input          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DRAM Training                      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Write leveling                     | 1                   | Enables Write Leveling calibration, which adjusts write DQS relative to the DDR clo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Read gate                          | 1                   | Enables Read Gate calibration, which adjusts valid RD DQS window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Read data eye                      | 1                   | Enables Read Data Eye calibration, which adjusts the read DQS to the center of rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQS to Clock Delay (ns)            | - I-                | Endoes read bata Eye calloration, which adjusts the read bags to the center of rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQ50                               | 0.0                 | DQS to Clock delay [0] (ns). The DQS path delay subtracted from the clock path delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DQS1                               | 0.0                 | DQS to Clock delay [1] (ns). The DQS path delay subtracted from the clock path del                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQS2                               | 0.0                 | DQS to Clock delay [2] (ns). The DQS path delay subtracted from the clock path del                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQS3                               | 0.0                 | DQS to Clock delay [3] (ns). The DQS path delay subtracted from the clock path del                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |